# Building Networks with Open, Reconfigurable Hardware

## 1<sup>st</sup> Asia NetFPGA Developer's Workshop

Monday, June 14, 2010

John W. Lockwood

HTTP://ALGO-LOGIC.COM

**letFPGA**

**CEO & Lead Consultant, Algo-Logic Systems**

With input from:

#### **NetFPGA Group, Stanford University**

Hardware and tools available for university programs thanks to grants, donations, and/or partnerships from:

Algo-Logic

## **NetFPGA's Defining Characteristics**

#### Line-Rate

- Processes back-to-back packets

- Without dropping packets

- At full rate of Gigabit Ethernet Links

- Operating on packet headers

- For switching, routing, and firewall rules

- And packet payloads

- For content processing and intrusion prevention

#### Open-source Hardware

- Similar to open-source software

- Full source code available

- BSD-Style License

- But harder, because

- Hardware modules must meeting timing

- Verilog & VHDL Components have more complex interfaces

- Hardware designers need high confidence in specification of modules

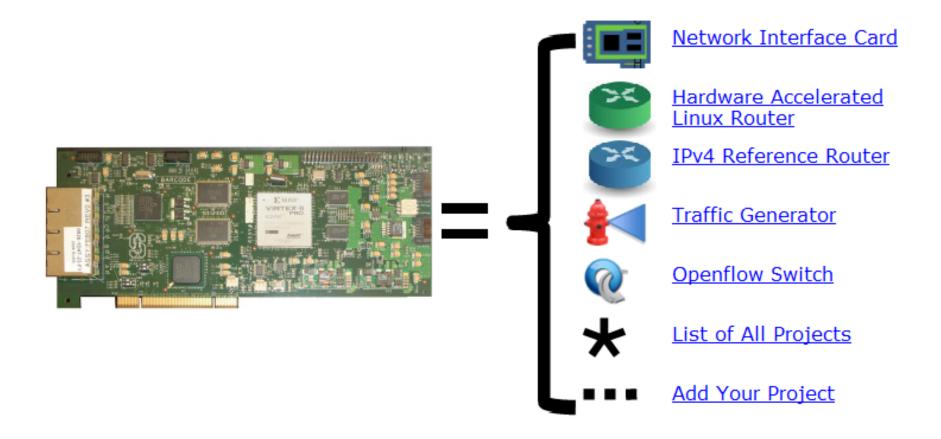

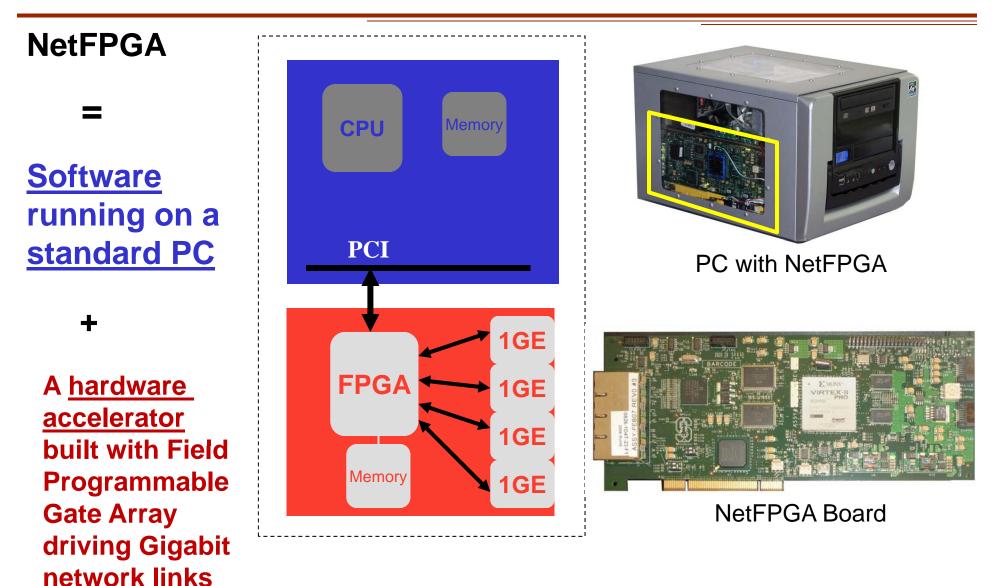

### **NetFPGA = Networked FPGA**

A line-rate, flexible, open networking platform for teaching and research

#### **NetFPGA Reference Platform**

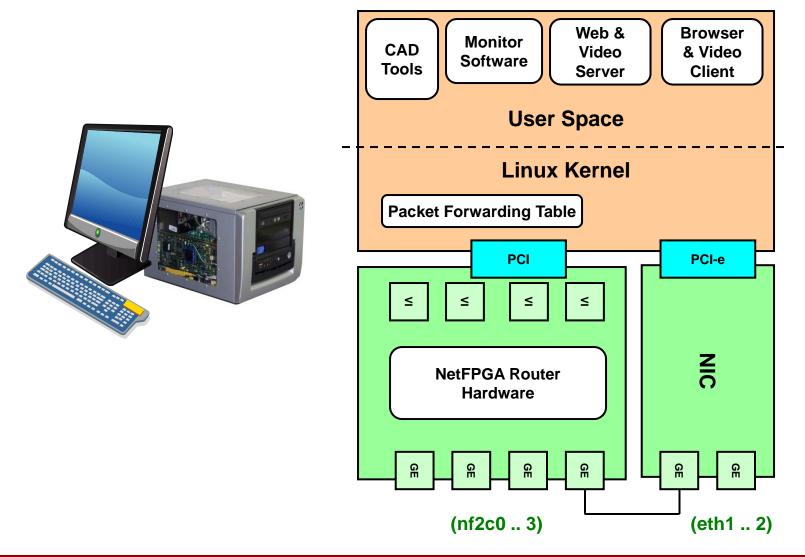

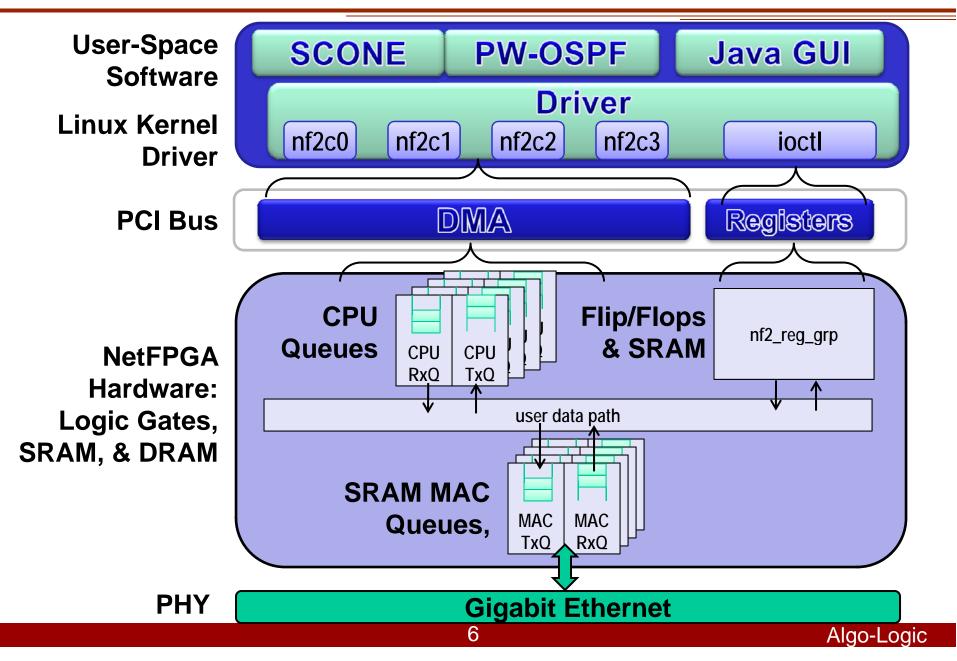

### **NetFPGA System**

### Hardware & Software Components

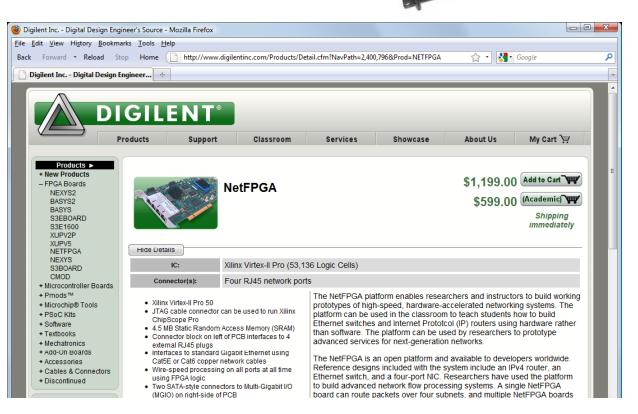

## **Open Platform, Low-cost Hardware**

#### NetFPGA Cards & Pre-built Systems

- Available from 3<sup>rd</sup> Party Vendors

- Or, build your system from parts

- Details in the on-line Guide

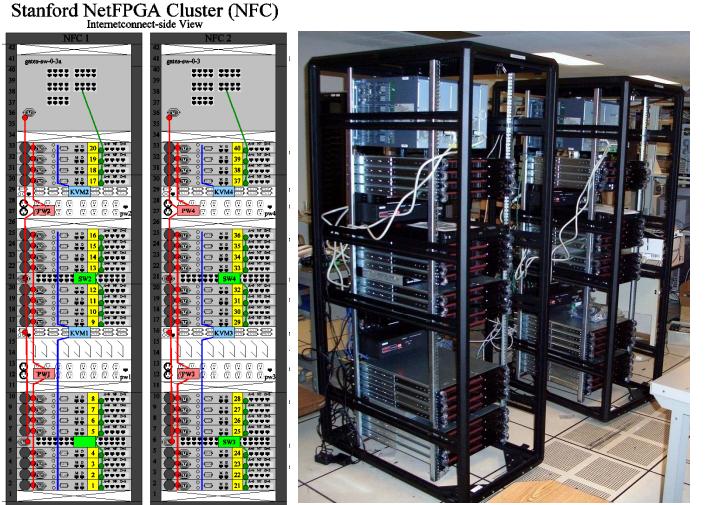

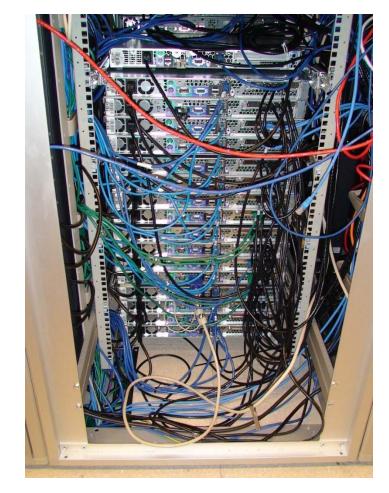

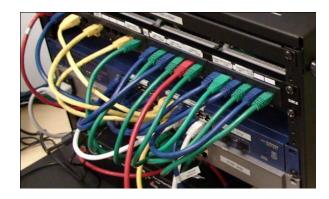

## **Stanford's Rackmount Deployment**

#### **Statistics**

- Rack of 40

- 1U PCs

- NetFPGAs

- Manged

- Power,

- Console

- VLANs

- Provides 160 Gbps of full line-rate processing bandwidth

### **UCSD's NetFPGA Cluster**

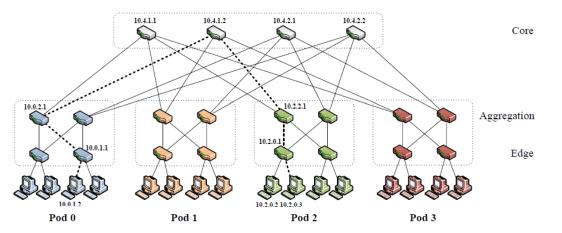

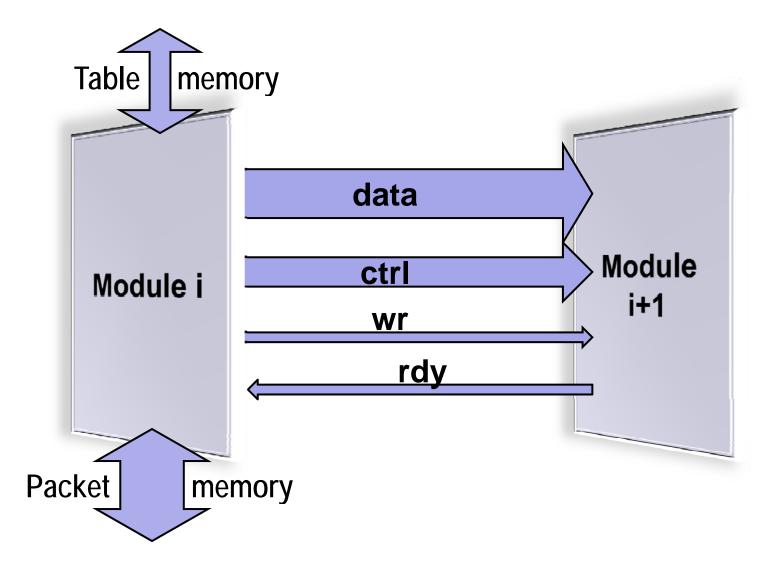

### **Inter-module Communication**

Algo-Logic

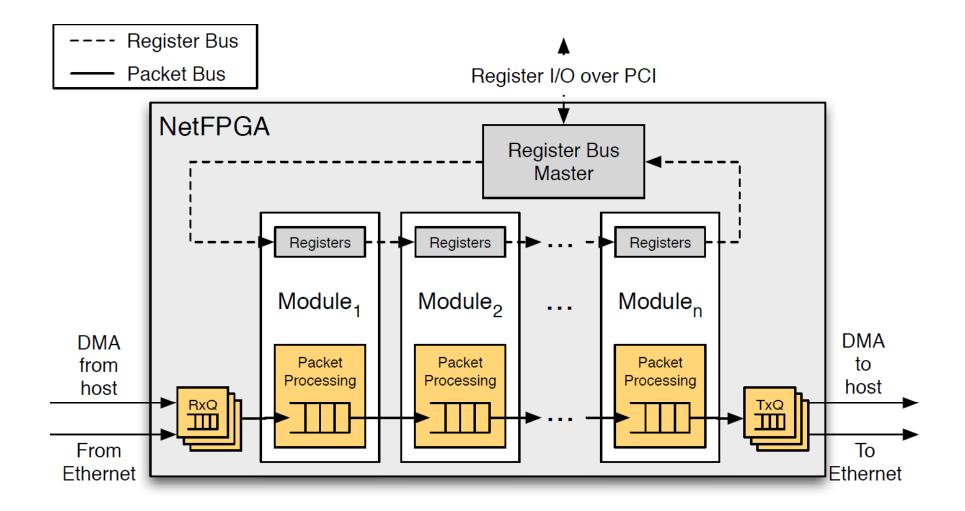

## **Modular Architecture**

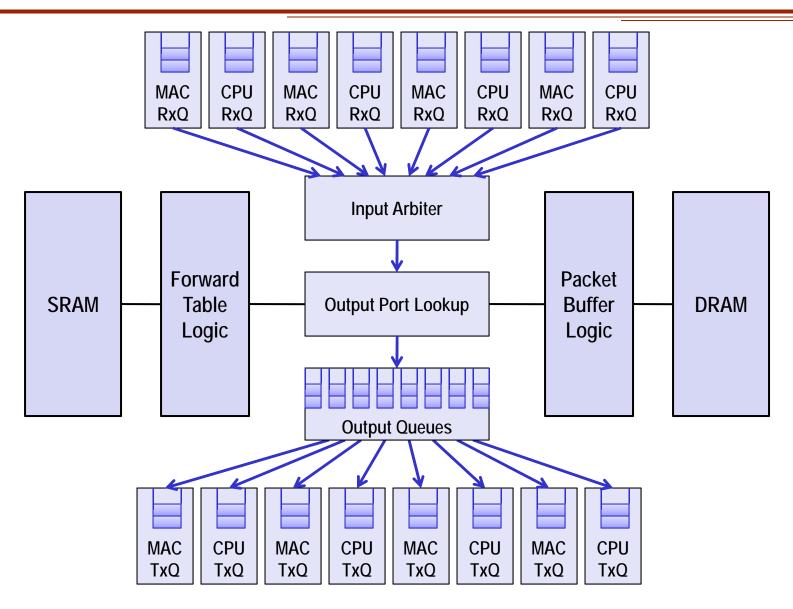

#### **NetFPGA Base** Reference Router

## **Reference Router Control Software**

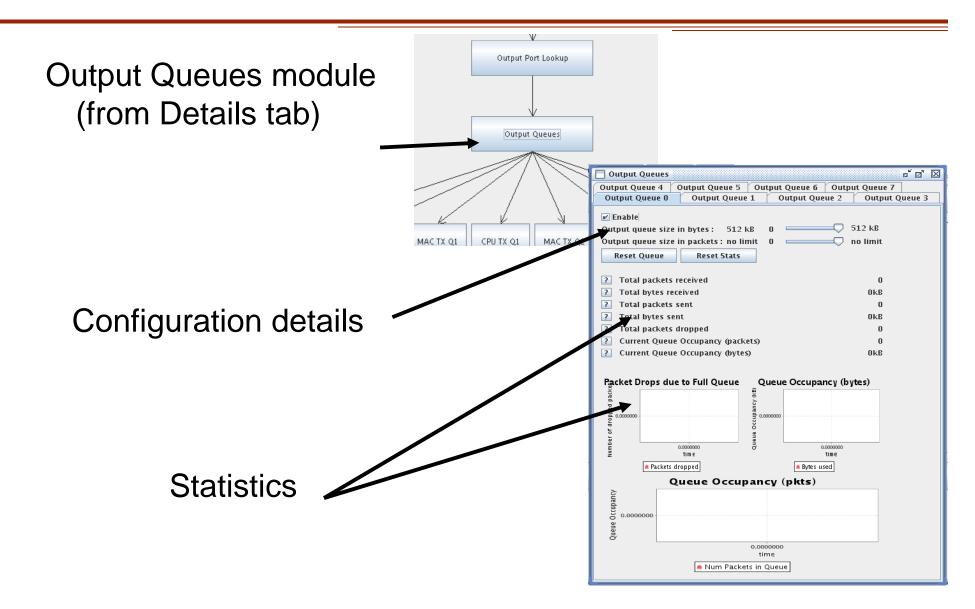

# Click the Details tab of the Quickstart window

This is the reference router pipeline – a canonical, simple-to-understand, modular router pipeline

| Router Quickstart                                                                                                                                                    |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Configuration Statistics Details                                                                                                                                     |  |

| Reset to Defaults         Output queue size in bytes :       value       0         Output queue size in packets :       value       0         Load From File       0 |  |

| uter Control Panel 🍥                                                                                                                                                 |  |

| Help Window                                                                                                                                                          |  |

| Router Quickstart                                                                                                                                                    |  |

| onfiguration Statistics Details                                                                                                                                      |  |

| MAC RX Q0 CPU RX Q0 MAC RX Q1 CPU RX Q1 MAC RX Q2 CPU RX Q2 MAC RX Q3 CPU RX Q3<br>Input Arbiter<br>Output Port Lookup                                               |  |

| Output Queues<br>Output Queues<br>MAC TX Q0 CPU TX Q1 MAC TX Q2 CPU TX Q2 MAC TX Q3 CPU TX Q3                                                                        |  |

## **Control Software - Continued**

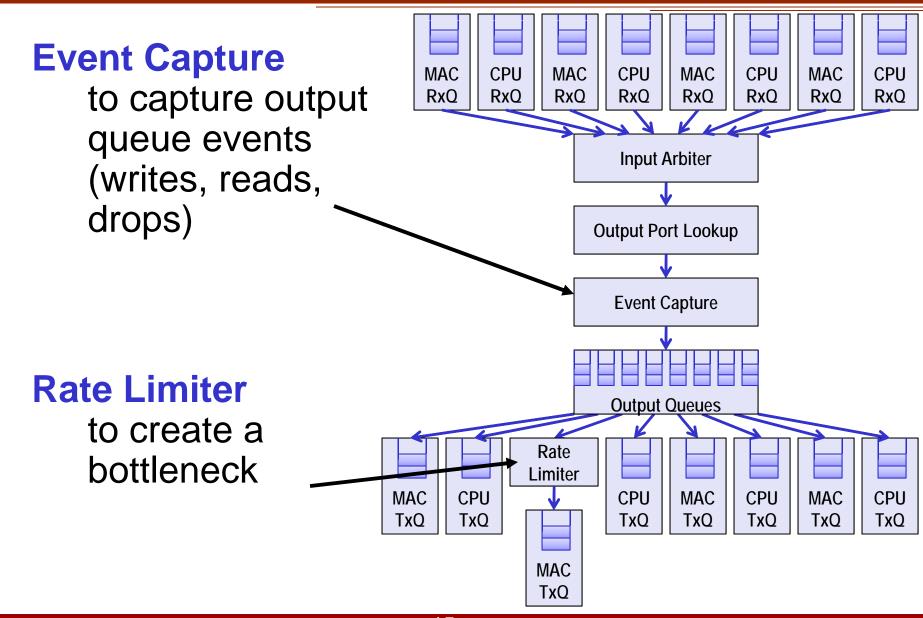

## **Enhanced Router Pipeline**

Algo-Logic

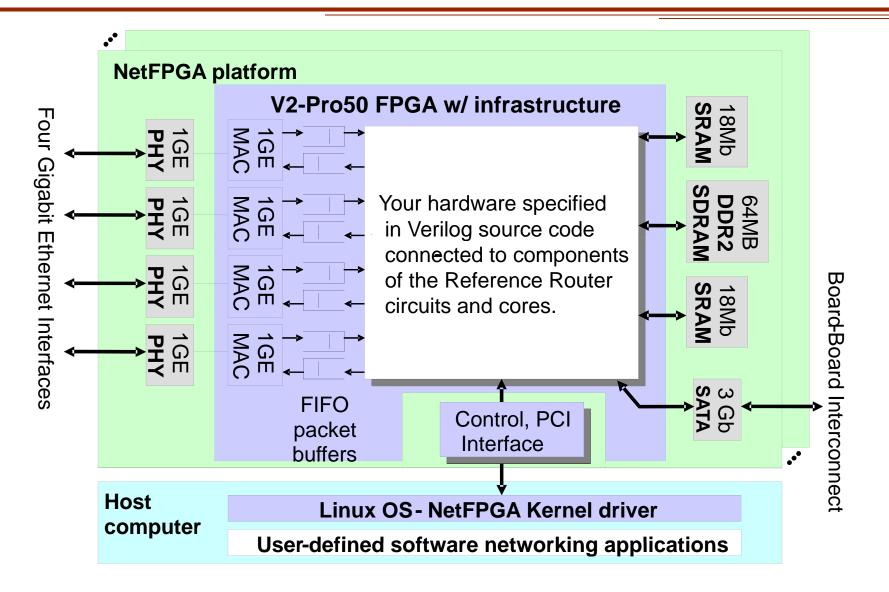

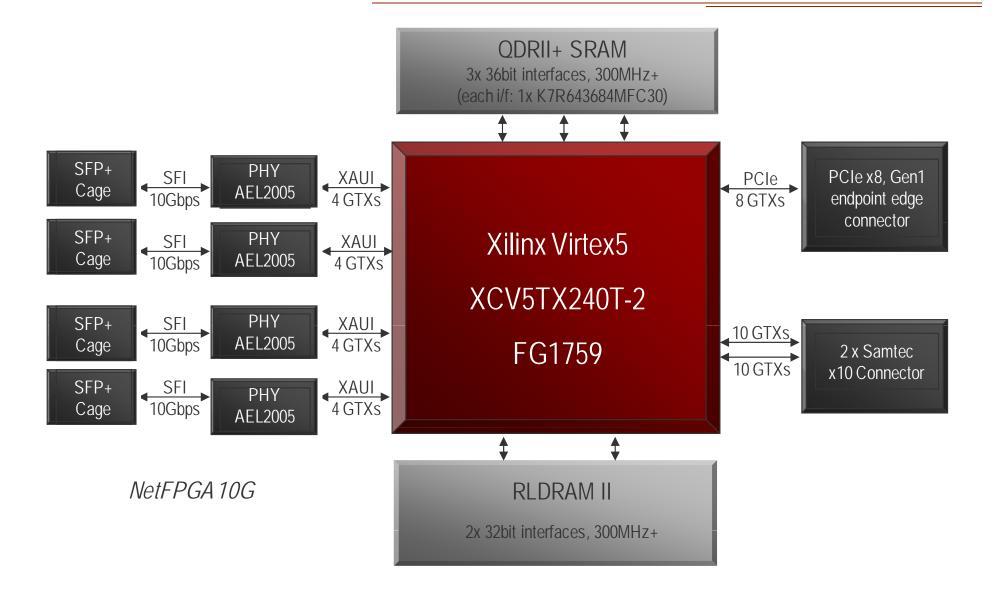

## **NetFPGA Hardware Block Diagram**

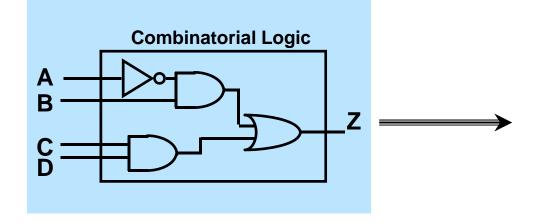

## Hardware Description Languages

#### • Concurrent

By default, Verilog statements evaluated concurrently

• Express fine grain parallelism

- Allows gate-level parallelism

- Provides Precise Description

- Eliminates ambiguity about operation

#### • Synthesizable

– Generates hardware from description

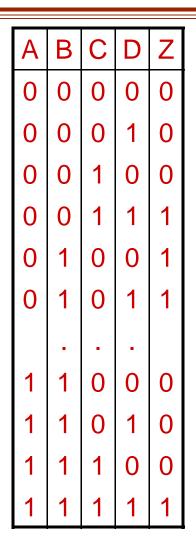

## **FPGA Look-Up Tables**

#### Combinatorial logic is stored in Look-Up Tables (LUTs)

- Also called

Function Generators (FGs)

- Capacity is limited only by number of inputs, not complexity

- Delay through the LUT is constant

**Diagram From: Xilinx, Inc**

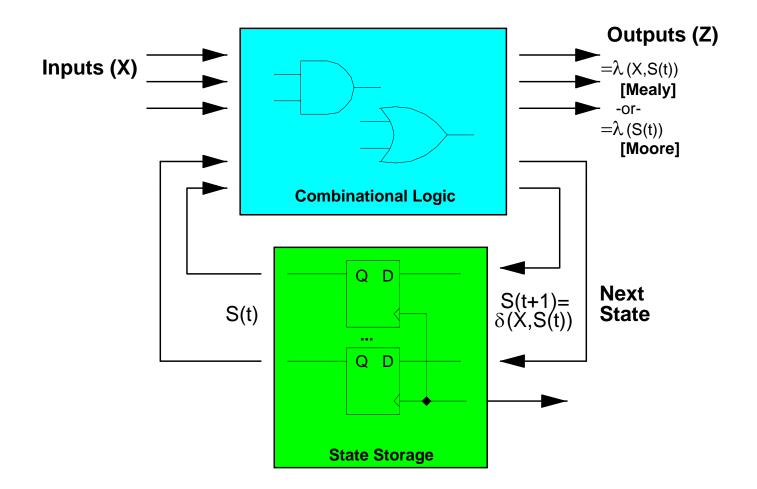

### **Finite State Machines**

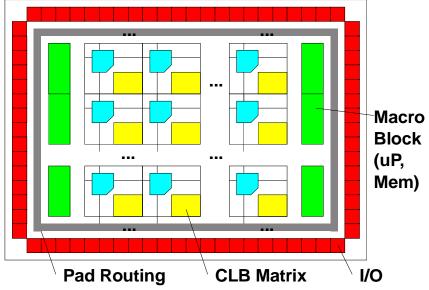

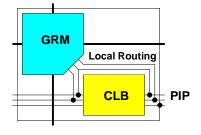

## **Field Programmable Gate Arrays**

#### CLB

- Primitive element of FPGA

#### **Routing Module**

- Global routing

- Local interconnect

#### **Macro Blocks**

- Block Memories

- Microprocessor

#### I/O Block

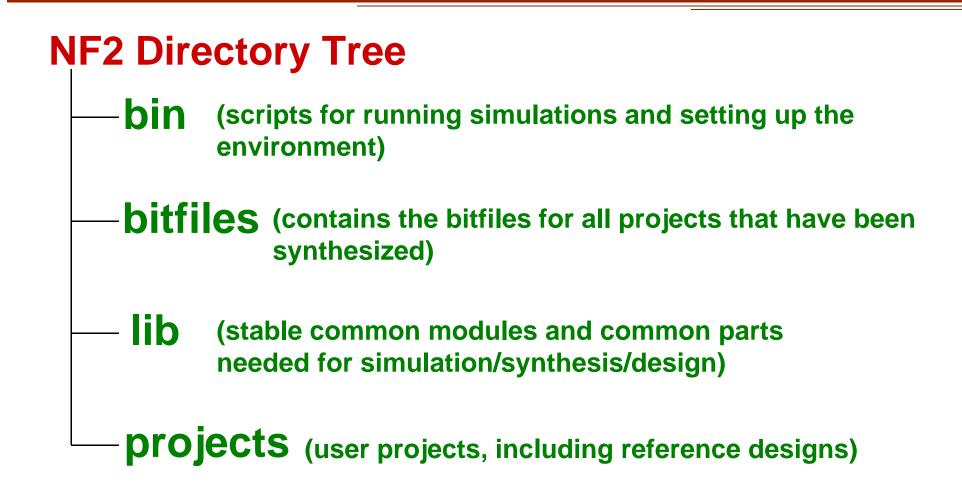

## **NetFPGA Reference Code & Modules**

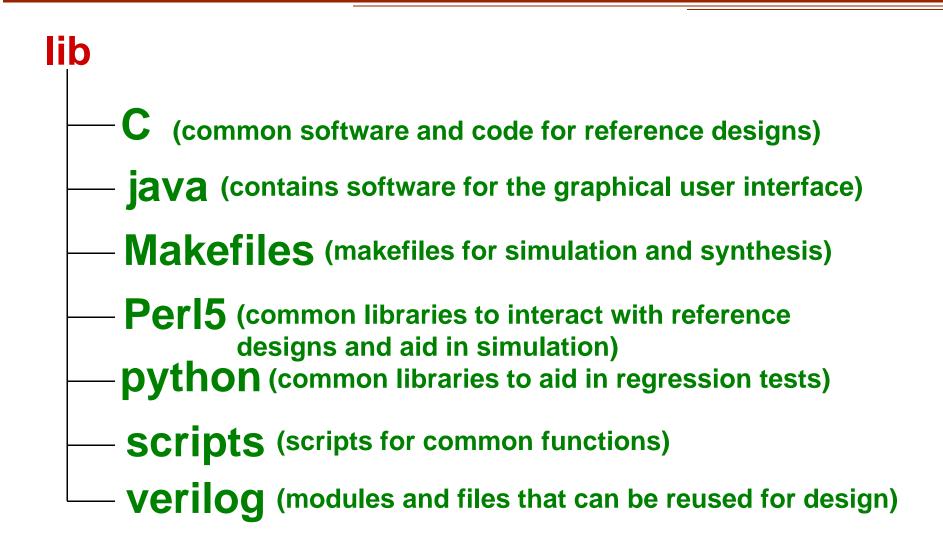

## **Structure of Libray Source Code**

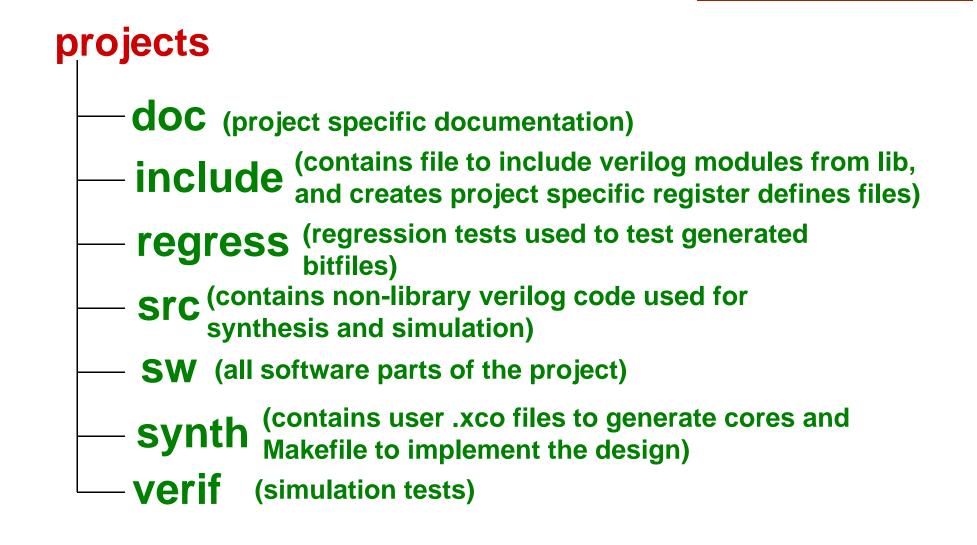

## **Structure of Project Source Code**

## **Test-Driven Designs**

#### Regression tests

- Have repeatable results

- Define the supported features

- Provide clear expectation on functionality

#### • Example: Internet Router

- Drops packets with bad IP checksum

- Performs Longest Prefix Matching on destination address

- Forwards IPv4 packets of length 64-1500 bytes

- Generates ICMP message for packets with TTL <= 1</li>

- Defines how packets with IP options or non IPv4

... and dozens more ...

Every feature is defined by a regression test

## **Welcome to the Worldwide Community**

NetFPGA @ SIGCOMM - Seattle, WA

NetFGPA @ SIGMETRICS - San Diego, CA

EuroSys - Glasgow, Scotland, U.K.

#### Workshop in Beijing, China

Workshop in Bangalore, India

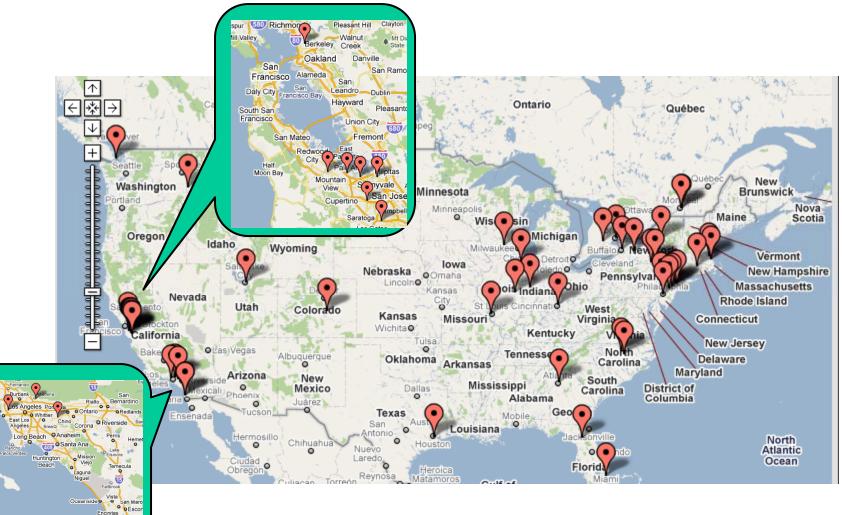

## **NetFPGA Deployments**

Over 1,350 NetFPGA users with 1,300+ cards deployed at 150+ universities in 17 Countries worldwide

**Worldwide Hardware Deployments - Feb 2010**

#### **NetFPGA Hardware in North America**

**USA Deployments - Feb 2010**

### **NetFPGA Hardware in Europe**

#### **European Deployments - Feb 2010**

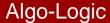

### **NetFPGA Hardware in Asia**

China, Korea, Japan, Taiwan, and India Deployments - Feb 2010

### **NetFPGA Deployments in Korea**

## **Contributed projects**

| Project (Title & Summary)         | Base<br>Version | Status     | Organization             | Documentat   |

|-----------------------------------|-----------------|------------|--------------------------|--------------|

| IPv4 Reference Router             | 2.0             | Functional | Stanford University      | Guide        |

| Quad-Port Gigabit NIC             | 2.0             | Functional | Stanford University      | Guide        |

| Ethernet Switch                   | 2.0             | Functional | Stanford University      | Wiki         |

| Buffer Monitoring System          | 2.0             | Functional | Stanford University      | Guide        |

| Hardware-Accelerated Linux Router | 2.0             | Functional | Stanford University      | Guide        |

| DRAM-Router                       | 2.0             | Functional | Stanford University      | <u>Wiki</u>  |

| DRAM-Queue Test                   | 2.0             | Functional | Stanford University      | Wiki         |

| Packet Generator                  | 2.0             | Functional | Stanford University      | <u>Wiki</u>  |

| OpenFlow Switch                   | 2.0             | Functional | Stanford University      | Wiki         |

| NetFlow Probe                     | 1.2             | Functional | Brno University          | <u>Wiki</u>  |

| AirFPGA                           | 2.0             | Functional | Stanford University      | Wiki and Pap |

| Fast Reroute & Multipath Router   | 2.0             | Functional | Stanford University      | <u>Wiki</u>  |

| NetThreads                        | 1.2.5           | Functional | University of Toronto    | Wiki         |

| Precise Traffic Generator         | 1.2.5           | Functional | University of Toronto    | <u>Wiki</u>  |

| URL Extraction                    | 2.0             | Functional | Univ. of New South Wales | Wiki         |

| zFilter Sprouter (Pub/Sub)        | 1.2             | Functional | Ericsson                 | <u>Wiki</u>  |

| Windows Driver                    | 2.0             | Functional | Microsoft Research       | Wiki?        |

#### ... continued on next page ...

#### As of Feb 2010

#### .. And more on <a href="http://netfpga.org/foswiki/bin/view/NetFPGA/OneGig/ProjectTable">http://netfpga.org/foswiki/bin/view/NetFPGA/OneGig/ProjectTable</a>

## **NetFPGA Designs (continued..)**

#### ... continued from previous page ...

| Windows Driver                              | 2.0   | Functional           | Microsoft Research                                 | Wiki?       |

|---------------------------------------------|-------|----------------------|----------------------------------------------------|-------------|

| RED                                         | 2.0   | Functional           | Stanford University                                | <u>Wiki</u> |

| Open Network Lab                            | 2.0   | Functional           | Washington University                              | <u>Wiki</u> |

| DFA                                         | 2.0   | Functional           | UMass Lowell                                       | Wiki?       |

| G/PaX                                       | ?.?   | Functional           | Xilinx                                             | <u>Wiki</u> |

| RCP Router                                  | 2.0   | Functional           | Stanford University                                | <u>Wiki</u> |

| Deficit Round Robin (DRR)                   | 2.0   | Functional           | Stanford University                                | Wiki        |

| OpenFlow-MPLS Switch                        | 2.0   | Functional           | Ericsson                                           | Wiki        |

| PTP-enabled Router                          | 2.0   | Functional           | Stanford University                                | <u>Wiki</u> |

| Vlan Tag Handler                            | 2.0   | Functional           | Stanford University                                | <u>Wiki</u> |

| Port Aggregator                             | 2.0   | Functional           | Stanford University                                | <u>Wiki</u> |

| IP Lookup w/Blooming Tree                   | 1.2.5 | In Progress          | University of Pisa                                 | <u>Wiki</u> |

| KOREN Testbed                               | ?.?   | In Progress          | Chungnam-Korea                                     | <u>Wiki</u> |

| Virtual Data Plane                          | 1.2   | In Progress          | Georgia Tech                                       | <u>Wiki</u> |

| Deficit Round Robin (DRR) Input Arbiter     | 1.2   | In Progress          | Universidade Federal do Rio Grande do Sul (Brazil) | <u>Wiki</u> |

| Counter Braids                              | 2.0   | Functional           | Stanford (Lu, Jianying)                            | <u>Wiki</u> |

| Tunneling NIC                               | 2.0   | In Progress          | Stanford                                           | Wiki        |

| Multicore Prototype for Real-Time Switching | 1.0   | Available on Request | University of Waterloo                             | <u>Wiki</u> |

| End-to-End Ethernet Authorization           | 2.0   | In Progress          | Euskal Herriko Unibertsitateko                     | Wiki        |

| Ultra-high Speed Congestion-control         | 2.0   | In Progress          | University of North Carolina                       | Wiki        |

|                                             |       |                      |                                                    |             |

#### .. And more on <a href="http://netfpga.org/foswiki/bin/view/NetFPGA/OneGig/ProjectTable">http://netfpga.org/foswiki/bin/view/NetFPGA/OneGig/ProjectTable</a>

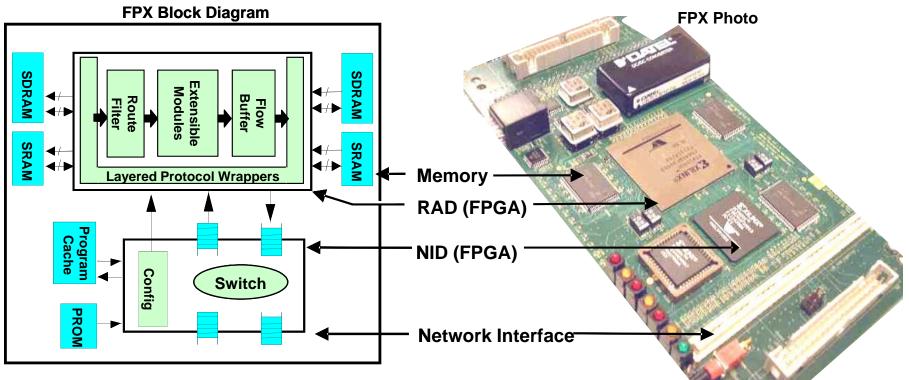

### **Other Network FPGA Platforms**

NetFPGA 1G

4 \* 1 GigE

4 Gbps

FPX

2 \* OC-48

4.8 Gbps

Upcoming 10G

4 \* 10GE

40 Gbps

## **Motivation for Network Security**

#### • Viruses can be costly to businesses

- Annoyance to average users

- Use networks to propagate

#### Sample Attacks

- Nimda, Code Red, Slammer

- MSBlast

- Infected over 350,000 hosts

- SoBigF

- Infected 1 million users in first 24 hours

- Infected > 200 million in the first week

- Caused an estimated \$1 billion in damages to repair.

#### • End-systems difficult to maintain

- Operating systems become outdated

- Users introduce new machines on network

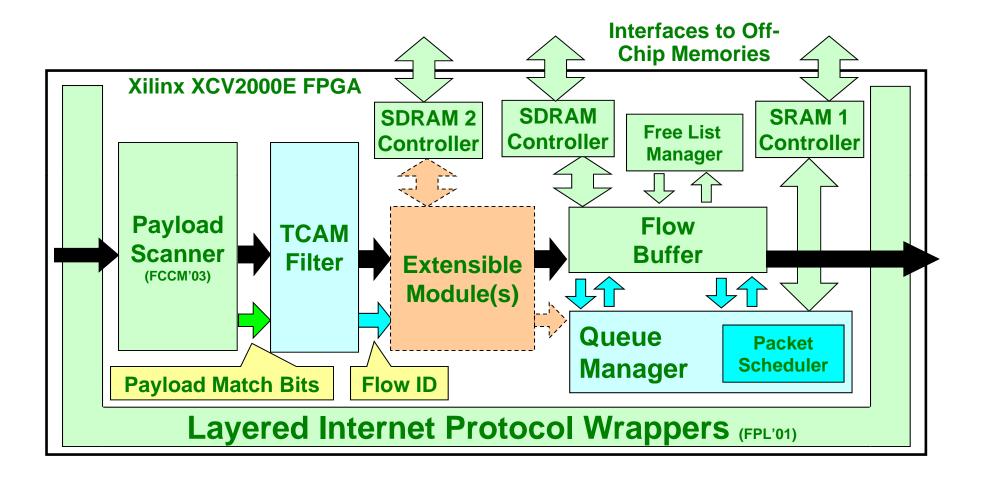

## **Example of SOC Firewall-FPX Platform**

#### • Reference

An Extensible, System-On-Programmable-Chip, Content-Aware Internet Firewall, by John W. Lockwood, Christopher Neely, Christopher Zuver, James Moscola, Sarang Dharmapurikar, and David Lim; Field Programmable Logic and Applications (FPL), Lisbon, Portugal, Paper 14B, Sep 1-3, 2003.

#### • More Information:

http://www.reprogrammablenetworks.com/

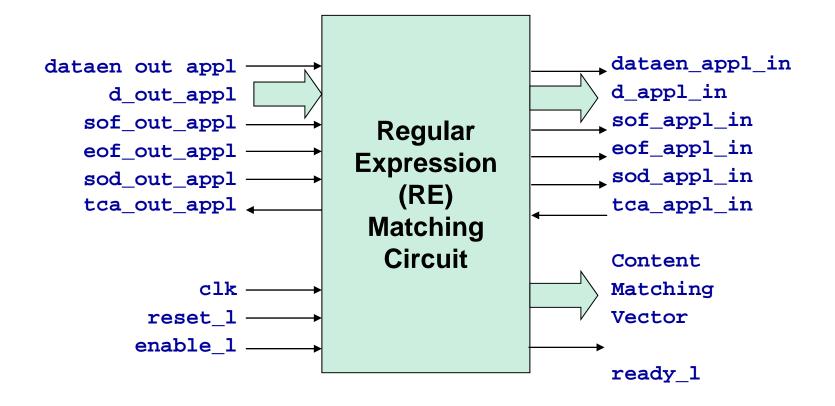

#### **Regular Expression Matching**

#### String Matching

- Allow for matching of fixed-length strings

- HEX(683063423739) finds SoBig.F

#### Regular Expressions

- Allows for a wide range of matches

- Case variations : (W|w)(A|a)(R|r)(H|h)(O|o)(L|I)

- Wild-card characters: Albert ? Einstein

- Strings of wildcards : A.\* Einstein

- Content may begin anywhere in packet

#### Morphable Patterns

- Will require systems that can evolve

## **GUI to Select Search Strings**

| 🚰 Online Support - Microsoft Internet Explorer                  |                                     |        |     |                                         |                               |            |        |   |  |  |

|-----------------------------------------------------------------|-------------------------------------|--------|-----|-----------------------------------------|-------------------------------|------------|--------|---|--|--|

| <u>File E</u> o                                                 | File Edit View Favorites Tools Help |        |     |                                         |                               |            |        |   |  |  |

| 🕞 Back 🝷 🕥 🗧 👔 🌠 🔎 Search 👷 Favorites 🔇 Media 🤣 🔗 🍓 📄 🗔         |                                     |        |     |                                         |                               |            |        |   |  |  |

| Address 🙆 http://192.168.50.50/view_property.php 🔹 🏹 Go Links 🎽 |                                     |        |     |                                         |                               |            |        |   |  |  |

| Select                                                          | Edit                                | Delete | Id  | Search String                           | Description                   | Author     | Value  |   |  |  |

|                                                                 | EDIT                                | DELETE | 17  | !HEX(6c744e5076)                        | Clear and Present Danger      | 9          | 3.00   |   |  |  |

|                                                                 | EDIT                                | DELETE | 6   | ViRuS                                   | An Email Virus                | 15         | 5.00   |   |  |  |

|                                                                 | EDIT                                | DELETE | 13  | Copyright .* WashU                      | WashU Copyright               | 12         | 1.00   |   |  |  |

|                                                                 | EDIT                                | DELETE | 128 | (L I)(A a)(D d)(E e)(N n)               | Terrorist Last Name           | 5          | 100.00 |   |  |  |

|                                                                 | EDIT                                | DELETE | 127 | (O o)sama                               | Terrorist First Name          | 5          | 5.00   |   |  |  |

|                                                                 | EDIT                                | DELETE | 112 | Patient (Confidential Record)           | Confidential Information      | 17         | 5.00   |   |  |  |

|                                                                 | EDIT                                | DELETE | 113 | Medical (Information Record)            | Medical Record                | 17         | 5.00   | ш |  |  |

|                                                                 | EDIT                                | DELETE | 114 | Do Not (Distribute Release)             | Confidential Information      | 17         | 5.00   |   |  |  |

|                                                                 | EDIT                                | DELETE | 129 | !HEX(1B688E6D)                          | Internet Worm                 | 19         | 6.00   |   |  |  |

|                                                                 | EDIT                                | DELETE | 130 | NASA (C c)<br>(onfidential ONFIDENTIAL) | Confidential Information      | 20         | 5.00   |   |  |  |

|                                                                 | EDIT                                | DELETE | 133 | !HEX(683063423739)                      | SoBigF Internet Worm (MIME64) | 16         | 11.00  |   |  |  |

|                                                                 |                                     |        |     |                                         |                               |            |        | • |  |  |

| ۲                                                               |                                     |        |     |                                         |                               | 🥑 Internet |        |   |  |  |

### **Compiler to build Parallel Scan Engines**

## **Content Matching Module**

## Sample ModelSim Waveform

| 🕂 wave - default                                                            |                             |                              |              |                   |                    |                     |                     |                |                  |              |               | □×       |

|-----------------------------------------------------------------------------|-----------------------------|------------------------------|--------------|-------------------|--------------------|---------------------|---------------------|----------------|------------------|--------------|---------------|----------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>I</u> nse                         | rt F <u>o</u> rmat <u>i</u> | <u>T</u> ools <u>W</u> indow |              |                   |                    |                     |                     |                |                  |              |               |          |

| 😅 日 🎒   👗 🖣                                                                 | a 🛍 🚧                       | 🔉 🔉 T= 🛨                     | Г            |                   |                    | Ŧ                   | X                   | 3+             |                  |              |               |          |

| <mark>, ready_l_out</mark><br>— INPUT<br><u></u> dataen_in<br><b>⊞</b> d_in | 1<br>0<br>00000000          | 00000322 (4500               | 0020 (00000) |                   | Src IP             |                     | it IP               |                | 12300001 (000080 | 20 (00000    | 000           |          |

| ば sof_in<br>eof_in<br>sod_in<br>tca_in<br>→ OUTPUT →→→→                     | 0<br>0<br>1                 |                              |              |                   |                    |                     |                     |                | TTL <            | > 0 =        | Src IP        |          |

| dataen_out<br>⊡ d_out<br>_ sof_out<br>_ eof_out                             | 0<br>00000000<br>0<br>0     | 0000000                      |              |                   |                    |                     |                     | (00000322 )/   | 15000020 (000000 | 00 (3F 12    | 2E3 (80FC9913 | <u>x</u> |

| sod_out<br>sod_out<br>tca_out<br>⊕– <mark>,</mark> data_flop                |                             | 00000000 (0000               | 0322 (45000  | <u>320 (00000</u> | 000 <u>(</u> 3F112 |                     |                     |                | 0000000 (123000  | 01 (00008    | 020 (00000000 |          |

| 📕 state                                                                     | idle                        | idle                         | <u>(ver</u>  | <u>(flags</u>     | <u>)(ttl</u>       | <u>(srcip_ttl_1</u> | <u>(dstip_ttl_2</u> | (ports ttl 3 ( | (xmit            | <u>(idle</u> |               | $\Box$   |

|                                                                             | 6000 ns<br>581 ns           | 6                            | DO           | 62                | )                  | 640                 |                     | 660            | 680              |              | 700           |          |

| •                                                                           | 4                           |                              |              |                   |                    |                     |                     |                |                  |              |               | $\geq$   |

| 585 ns to 706 ns                                                            |                             |                              |              |                   |                    |                     |                     |                |                  |              |               | - //     |

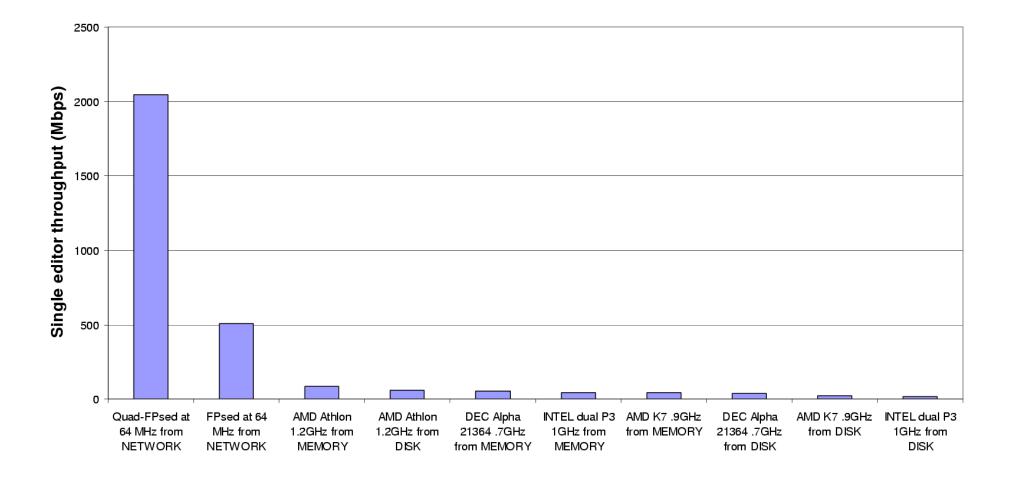

## **Throughput Comparison**

- Sed was run on different Linux PCs

- Dual Intel Pentium III @ 1 GHz

- 13.7 Mbps when data is read from disk

- 32.72 Mbps when data is read from memory

- Alpha 21364 @ 667 MHz

- 36 Mbps when data is read from disk

- 50.4 Mbps when data is read from memory

- Software results are 40x slower than FPsed

# **String Processing Benchmarks**

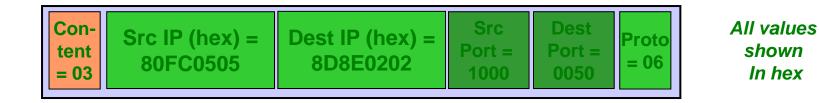

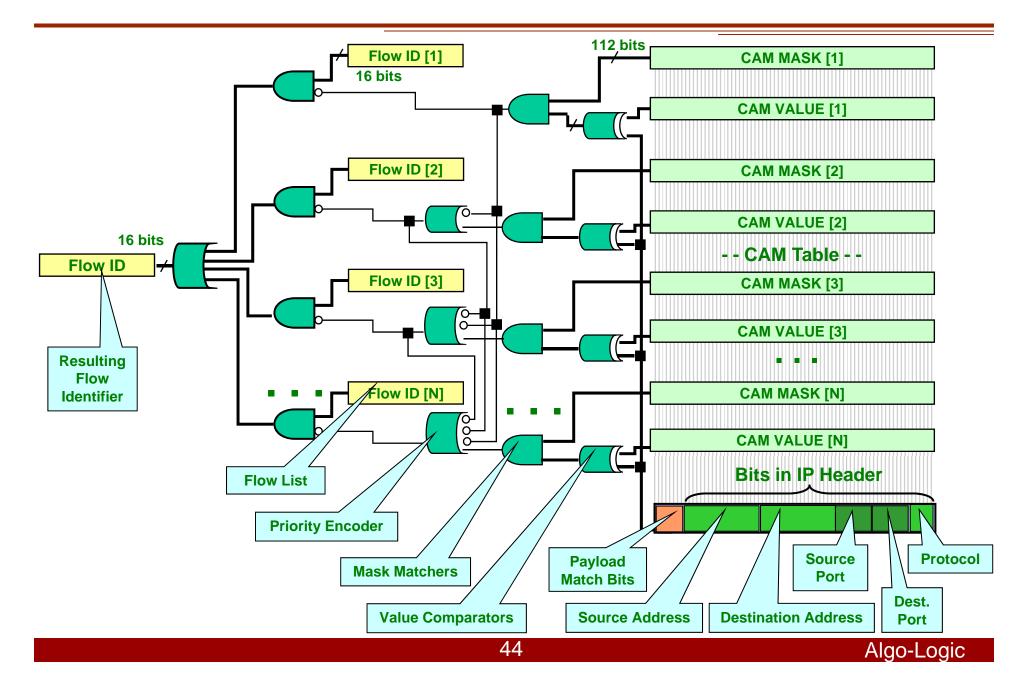

# **Associative Match in FPGA TCAM**

- **Content :** Content Vector = "00000011" (*binary*) = x"03" (*hex*)

- Source IP Address : 128.252.5.5 (dotted.decimal)

- **Destination IP Address**: 141.142.2.2 (dotted.decimal)

- Source Port : 4096 (decimal) = 1000 (hex)

- **Destination Port** : 80 (decimal) = 50 (hex)

- Protocol : TCP (6)

## **TCAM Function in FPGA Hardware**

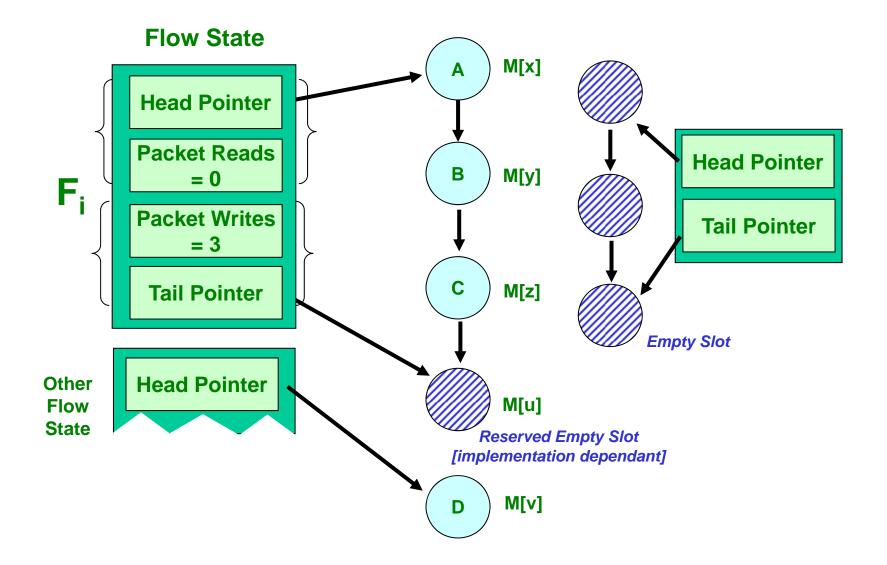

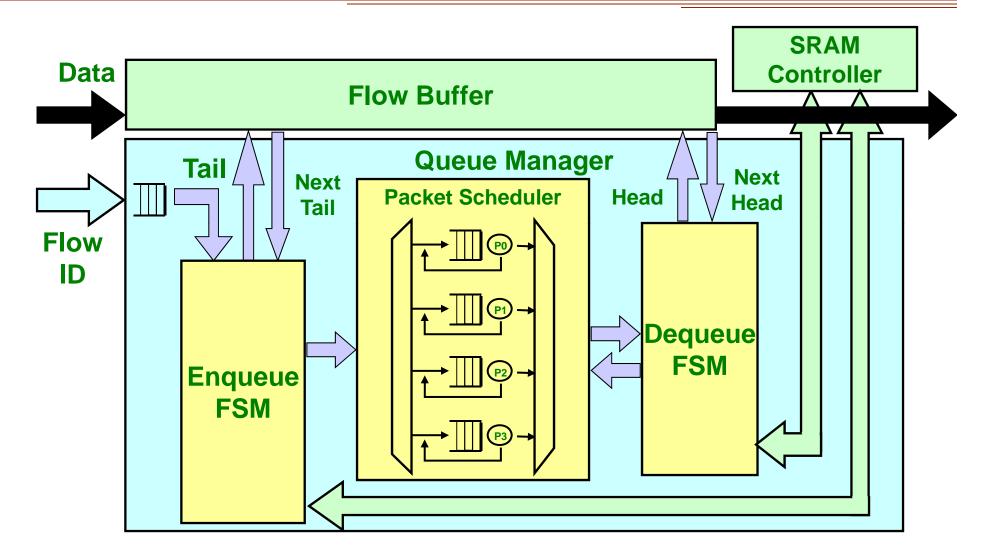

## **Data Buffering & Per-flow Queuing**

#### • Flow Buffering

- Maintain linked list of packets

- Track head and tail pointers for each list

- Track free memory

### Queue Management

- Enqueue packet

- Dequeue packet

### Schedule Traffic Flows

## **Flow Buffering**

### **Queue Management**

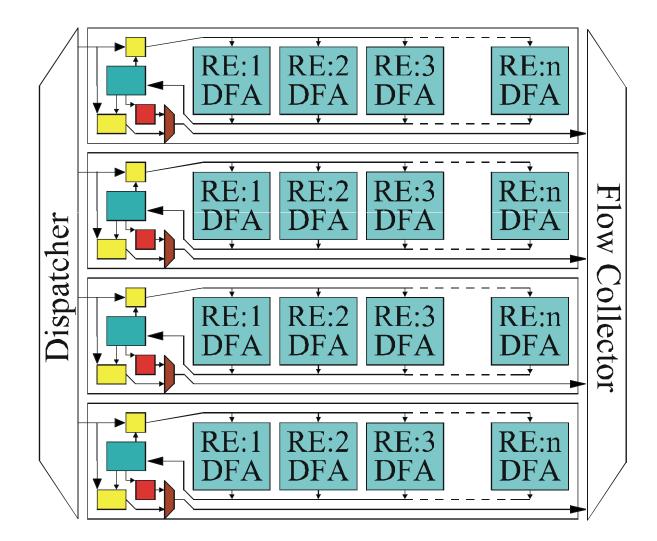

## **Architecture of the SOC Firewall**

### **Resulting SOC-Firewall FPGA Layout**

| 지원 전원 전 그는 바람이 나는 것을 가지 않는 것이다.                                     | ayered Proto<br>Vrappers | )col                         | Per-fi<br>Queu |                      |

|---------------------------------------------------------------------|--------------------------|------------------------------|----------------|----------------------|

| Regular Expression<br>Payload Filtering<br>TCAM Header<br>Filtering |                          | Region for Ex<br>Plug-in Mod |                | Packet Store Manager |

## Upcoming NetFPGA 10G (4 \* 10 GE)

### **40 Gbps NetFPGA PCB**

## **Algo-Logic Systems**

Founded by Dr. John W. Lockwood, the Algo-Logic ® team has extensive experience building routers, data center switches, and network processing circuits in ASICs and FPGA logic. Algo-Logic specializes in mapping network algorithms into hardware logic. The founders are experts in developing, documenting, and prototyping logic and systems of reprogrammable networks.

- http://Algo-Logic.com

- Email

- Solutions@Algo-Logic.com

- Phone

- (650) 395-7026

- Fax

- (650) 498-8296

- Office Address

- 530 Lytton Ave

Second Floor

Palo Alto, CA 94301

## **Consulting Services**

- Design and Build Hardware-Accelerated Network Systems

- Network Architecture

- Data-center networks

- Network security

- Content-aware networks

- On-chip interconnect

- Performance Analysis

- Mathematical system modeling

- Real and synthetic trace simulation

- Live measurements in hardware prototypes

## **Design Services**

#### • Implementations of Network Algorithms

- Hardware Logic in synthesizable high-level HDLs, Verilog, and VHDL

- Ultra low latency processing

- System-level software with APIs in C and C++

#### Architectures for Next-Generation Network

- Data-center networks

- Trading-floor networks

- Network security

- Content-aware networks

#### • Systems Architecture and Development

- FPGA design

- Verification and test bench development

- Customization of IP cores

- System-level Integration

Design, develop, and verify line-rate network processing systems at multi-Gbps rates.

# **Extended Training**

- Customized training services to help your team build your own network systems in hardware.

- Experience in teaching the world-wide NetFPGA tutorials

- Customized training specifically tailored for your company's skill level and requirements

- Hands-on training with live hardware systems

## **1st Asia NetFPGA Developer Workshop**

#### June 13-14, 2010 @ KAIST, Daejeon, Korea

http://fif.kr/AsiaNetFPGAws

#### • Program Committee Chairs

- John W. Lockwood

- (Algo-Logic Systems)

- Seung-Joon Seok

- (Kyungnam University)

#### Local Arrangement Co-Chairs

- Sue Moon

- (KAIST)

- Jaeyong Lee

- (Chungnam National Univ.)

- Advisory

- Nick McKeown

- (Stanford University)

- Dae Young Kim

- (Chungnam University)

#### • Many Thanks

- Xilinx

- NetFPGA Group

- Sponsors:

Algo-Logic

# **Program Committee Members**

- Jun Bi

- (Tsinghua University)

- Gordon Brebner

- (Xilinx)

- Michael Ciesla

- (UNSW)

- Yu-Huang Chu

- (Chunghwa Telecom)

- Sun Moo Kang

- (NIA)

- Eric Keller

- (Princeton University)

- Jongwon Kim

- (GIST)

- Taekyoung Kwon

- (Seoul National Univ.)

- Martin Labrecque

- (University of Toronto)

- Yukuen Lai

- (Chung-Yuan Christian Univ.)

- Jaeyong Lee

- (Chungnam National Univ.)

- John W. Lockwood

- (Algo-Logic Systems)

- Kevin Xie

- (Xilinx)

- Sue Moon

- (KAIST)

- Andrew, W. Moore

- (Cambridge University)

- Akihiro Nakao

- (University of Tokyo)

- Seung Yeob Nam

- (Yeungnam University)

- Seung-Joon Seok

- (Kyungnam University)

- Seung-Yong Park

- (Yonsei University)

- Hwangjun Song

(POSTECH)

- Charlie Wiseman

- (Washington University)

- Chong Ho Yoon

- (Korea Aerospace Univ.)

- Martin Zadnik

- (Brno University of Tech.)

- Hongyi Zeng

- (Stanford University)

- Young Cho

- (USC-ISI)

### Welcome